发布时间:2024-04-15 | ![]() 浏览量:201

浏览量:201

技术领域

本发明涉及半导体电子器件技术领域,具体涉及一种Trench MOS器件及其制备方法。

背景技术

Trench MOS器件是一种新型垂直结构器件,是在VDMOS(垂直双扩散金属氧化物半导体场效应晶体管)的基础上发展起来的,和VDMOS相比,Trench MOS具有更低的导通电阻和栅漏电荷密度,因此具有更低的导通和开关损耗和更快的开关速度。同时由于TrenchMOS器件的沟道是垂直的,故可进一步提高其沟道密度,减小芯片尺寸。

目前比较常见的Trench MOS器件的源极是通过在外延衬底的金属区域刻蚀通孔,沉积金属,以连接源极,将源极接出,但是为了避免寄生三极管效应,通孔一般会刻蚀至阱区,并且在沉积金属之前先要进行离子注入,减少金属与源极的接触电阻。

但是,沉积金属之前的离子注入与阱区的掺杂离子为同类型的掺杂,当在沉积金属之前进行离子注入时,由于通孔深度变深,阱区的掺杂会下阔,形成凸起,减少抗压外延衬底的厚度,结曲率半径变小,造成BV(击穿电压)下降。

发明内容

针对现有技术的不足,本发明的目的在于提供一种Trench MOS器件及其制备方法,旨在解决沉积金属之前注入与阱区的掺杂离子为同类型的掺杂,由于工艺波动所引起的通孔深度变化而导致阱区的掺杂下阔,使PN结形成曲率半径较小的凸起,造成BV下降的技术问题。

本发明的一方面在于提供一种Trench MOS器件的制备方法,Trench MOS器件的制备方法包括:

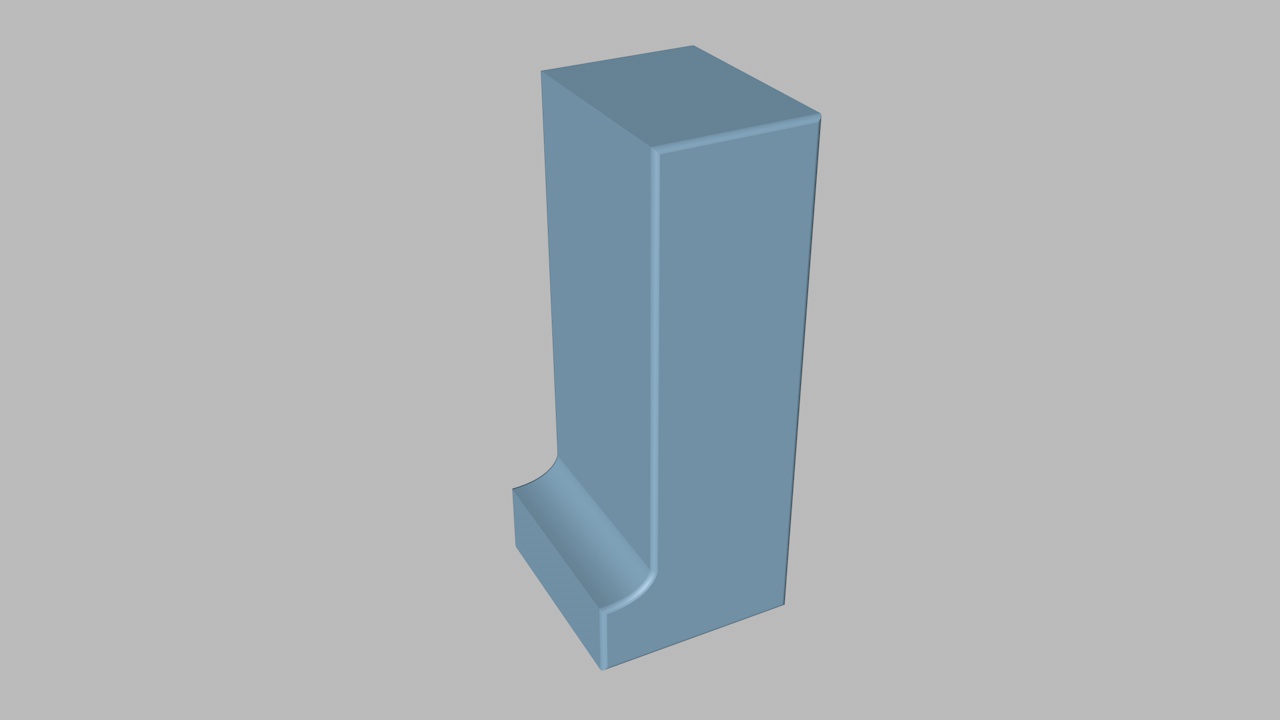

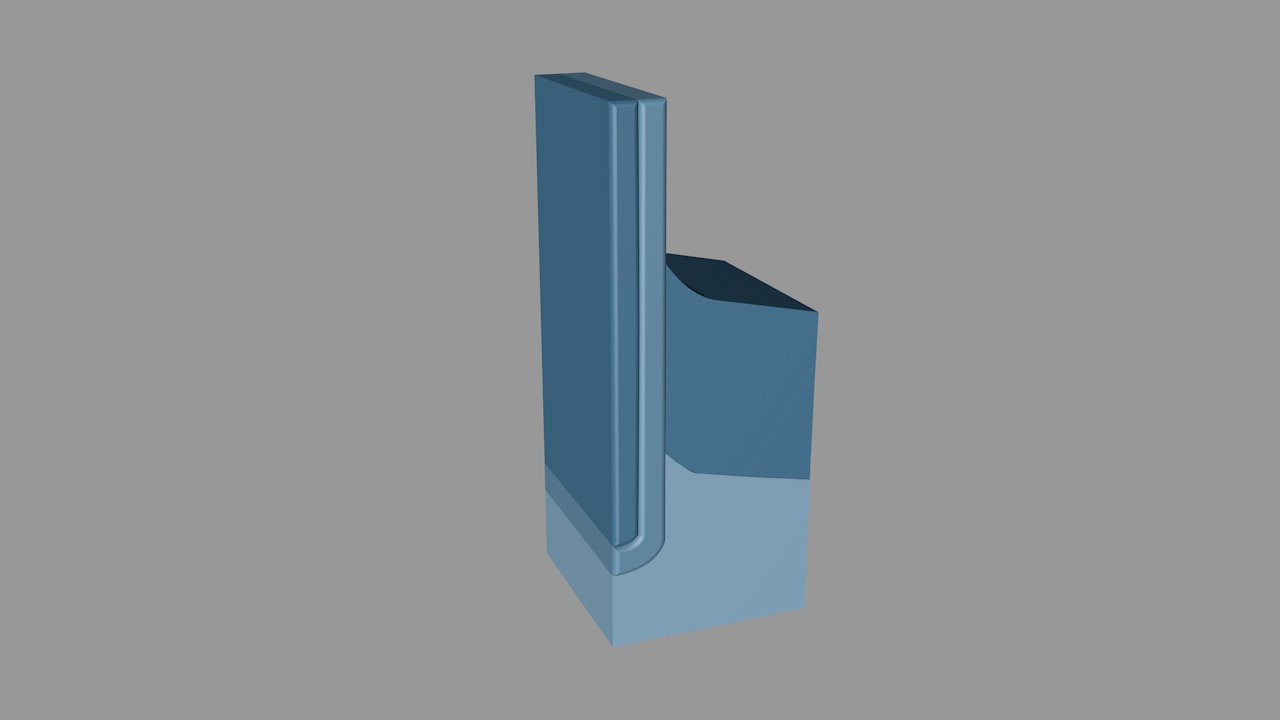

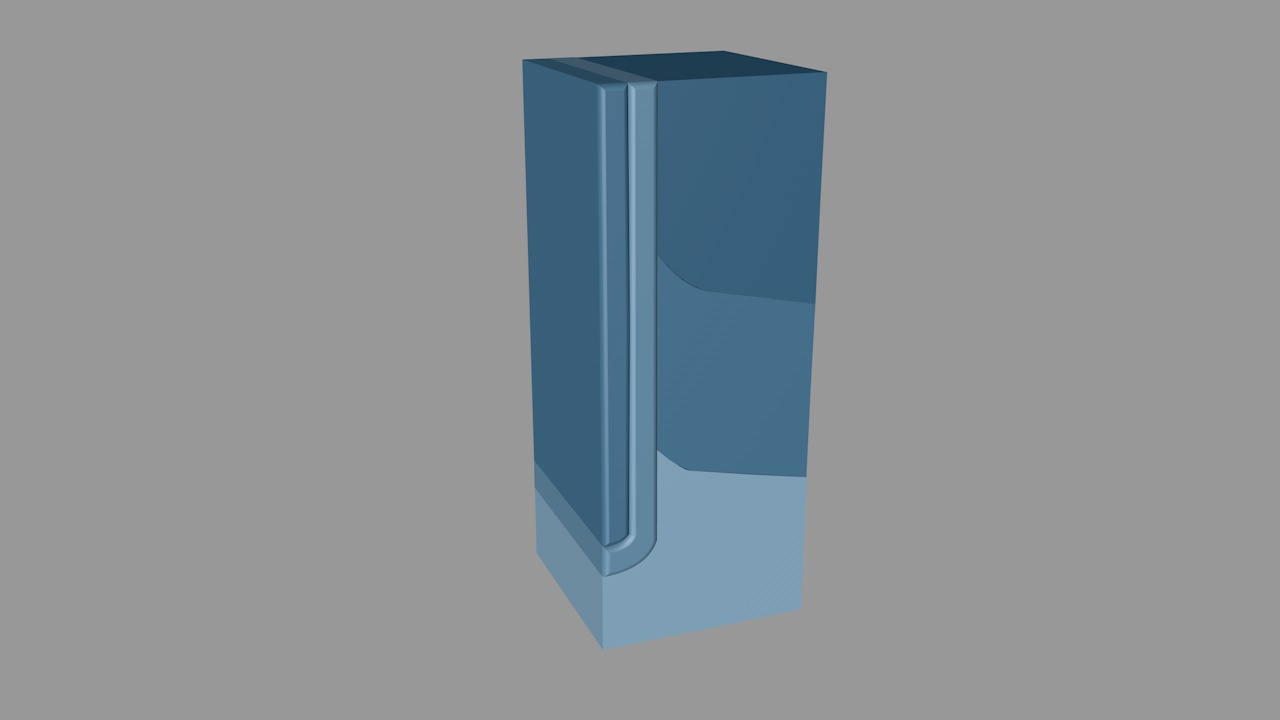

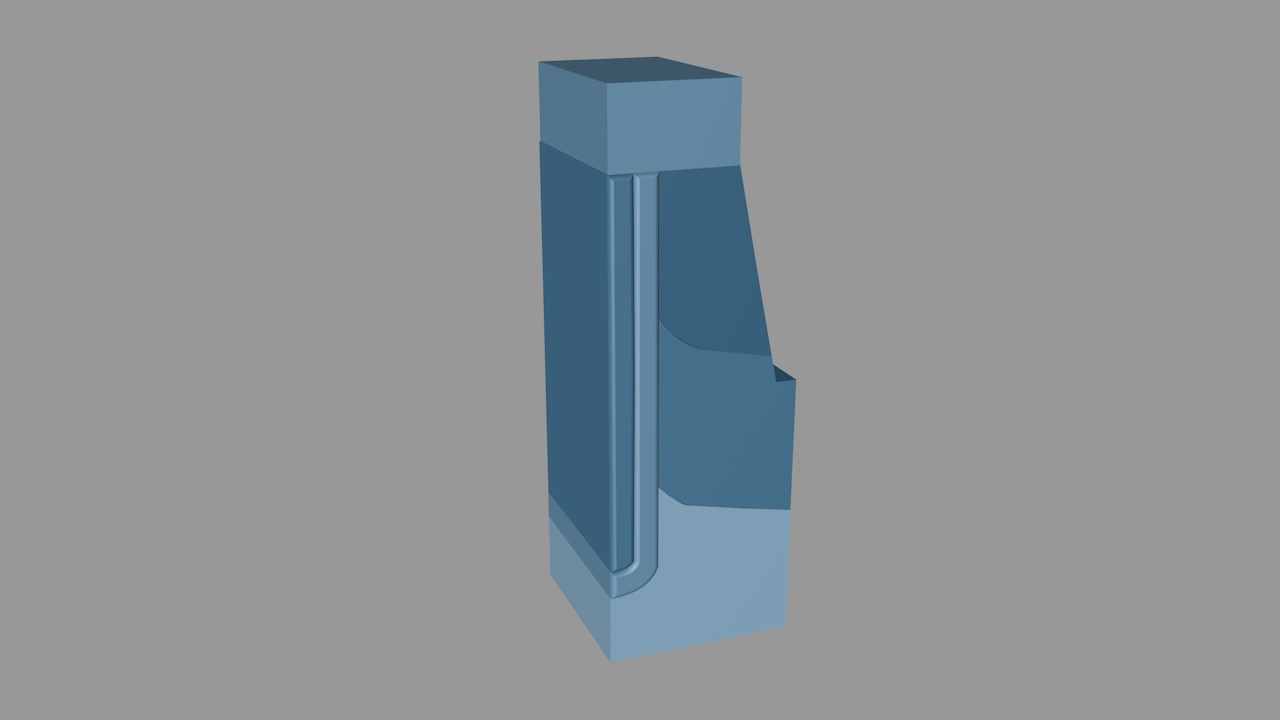

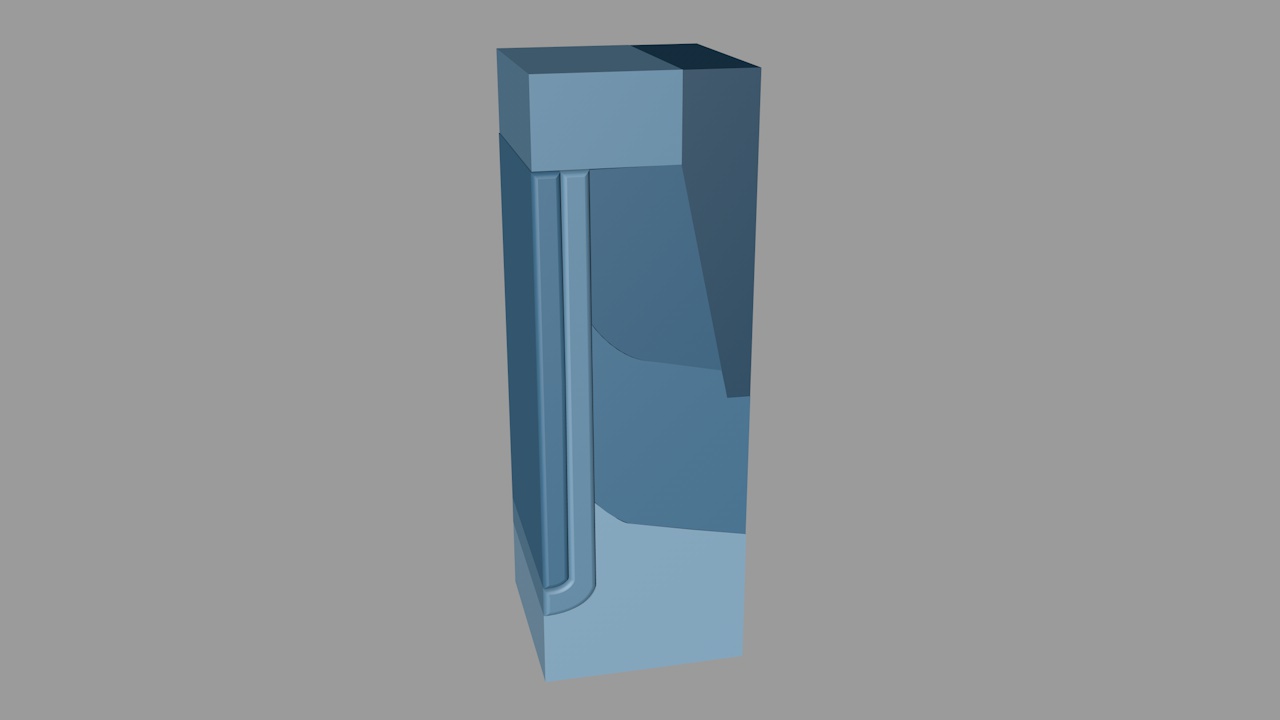

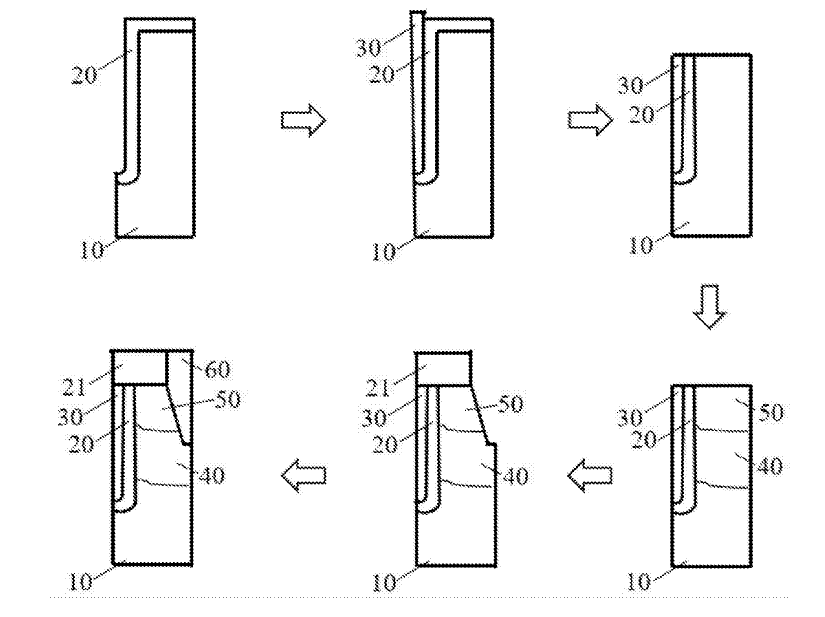

1、提供一P型外延衬底,并在P型外延衬底上刻蚀形成沟槽,在P型外延衬底的表面和沟槽上沉积预设厚度的第一介质层20。沟槽的深度为1μm-1.5μm。预设厚度为400Å-700Å。当预设厚度太薄时,无法有效地隔离衬底与栅极,造成短路。第一介质层20的生长温度为800℃-1100℃,通过热氧和高温的方式,能提高第一介质层20的致密性和平整性。

2、在沟槽内的第一介质层上生长多晶硅,以将沟槽填满,并将多晶硅30进行磨平回刻。多晶硅30磨平回刻后,形成栅极,避免多晶硅30残留于P型外延衬底10的表面造成短路。

3、在P型外延衬底于靠近沟槽的侧壁的一侧依次进行N型掺杂和P型掺杂,得到阱区和源极,源极设于阱区之上。具体细分为:

(1)对P型外延衬底10进行N型掺杂,掺杂剂为磷,N型掺杂的温度为700℃-1000℃,得到阱区40;其中,N型掺杂的浓度为1×1010cm-3-1×1014cm-3。

(2)对P型外延衬底10进行P型掺杂,掺杂剂为硼,P型掺杂的温度为800℃-1100℃,得到源极50。其中,P型掺杂的浓度为1×1013cm-3-1×1017cm-3。

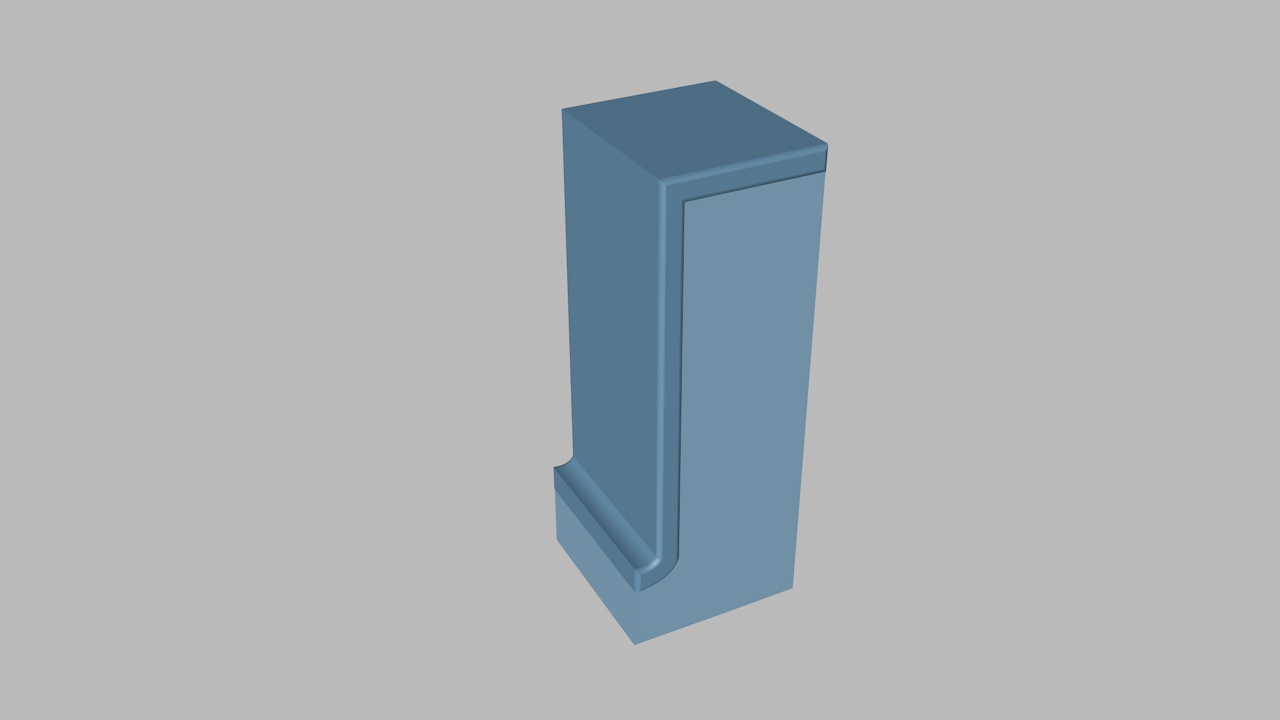

4、在P型外延衬底的表面沉积第二介质层,于靠近沟槽的一侧刻蚀第二介质层至阱区,形成凹槽。凹槽的深度为0.3μm-0.6μm。用于沉积金属60,将源极50导通接出,但是为了避免寄生三极管效应,凹槽一般会刻蚀至阱区40。

5、在凹槽内以第一预设温度、第一预设浓度进行P型离子注入,待P型离子注入完成后,以第二预设温度、第二预设浓度进行N型离子注入。具体细分为:

(1)P型离子为硼离子,第一预设温度为800℃-1100℃,第一预设浓度为1×1012cm-3-1×1015cm-3。通过第一预设温度和第一预设浓度的设置,以控制P型离子的扩散区域。扩散区域太宽,会影响阈值电压,扩散区域太深,将会导致源极50区域短路。

当第一预设浓度太低时,抑制N型离子的扩散有限,阱区40下阔形成凸起,导致BV下降;当第一预设浓度太高时,导致P型离子的扩散区域变宽变深,影响阈值电压或造成源极50短路。

同理,当第一预设温度过低时,P型离子的扩散区域有限,抑制N型离子的扩散有限,阱区40下阔形成凸起,导致BV下降;当第一预设温度太高时,导致P型离子的扩散区域变宽变深,影响阈值电压或造成源极50短路。

(2)在预设次数下,N型离子为砷离子,第二预设温度为700℃-1100℃,第二预设浓度为1×1013cm-3-1×1016cm-3。N型离子和P型离子均是通过凹槽的底部边缘注入。

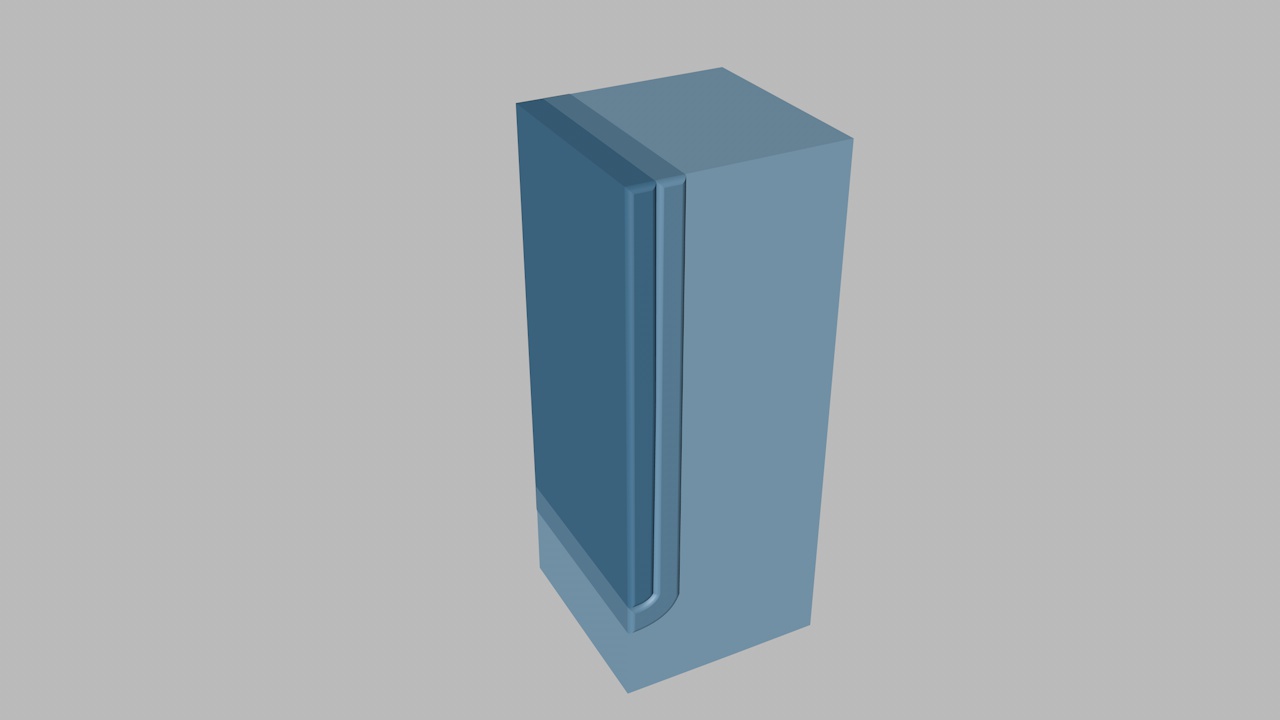

说明:为了减少金属60与源极50之间的接触电阻,需要在沉积金属60之前注入与阱区40的掺杂离子为同类型的掺杂,进行N型离子注入。但是,N型离子与阱区40的掺杂离子类型相同,将会导致阱区40的掺杂下阔,形成凸起,减少抗压外延衬底的厚度,结曲率半径变小,造成BV的下降。因此,在N型离子注入之前,注入P型离子,以抑制N型离子的扩散,使得阱区40平滑,改善凸起的形成,从而抑制BV的下降。

6、待N型离子注入完成后,在凹槽内沉积金属。

有益效果:

与现有技术相比,本发明的有益效果在于,解决了沉积金属之前注入与阱区的掺杂离子为同类型的掺杂,由于工艺波动所引起的通孔深度变化而导致阱区的掺杂下阔,使PN结形成曲率半径较小的凸起,造成BV下降的技术问题。

元器件符号说明:

P型外延衬底10,第一介质层20,第二介质层21,多晶硅30,阱区40,源极50,金属60。

具体实施方式

项目 | 凹槽的深度(μm) | BV值(V) |

实施例1 | 0.3 | 35.7 |

实施例2 | 0.4 | 35.2 |

实施例3 | 0.5 | 35.3 |

实施例4 | 0.6 | 35.2 |

对比例1 | 0.3 | 35.4 |

对比例2 | 0.4 | 34.8 |

对比例3 | 0.5 | 34.1 |

对比例4 | 0.6 | 33.2 |

根据上表实施案例数据可知,凹槽的深度越深,刻蚀到阱区的深度越深,注入的N型离子越容易造成阱区下阔,凸起越大,BV下降越多,当在N型离子之前注入P型离子,能有效地抑制阱区下阔,抑制凸起的产生,提升BV。此外,凹槽越深,P型离子的抑制作用越明显。