发布时间:2024-04-15 | ![]() 浏览量:307

浏览量:307

技术领域

本发明涉及半导体器件制造的技术领域,特别涉及一种改善SGT阈值电压稳定性的工艺方法及SGT器件。

背景技术

MOSFET大致可以分为以下几类:平面型MOSFET;Trench (沟槽型)MOSFET,主要用于低压领域;SGT(Shielded Gate Transistor,屏蔽栅沟槽)MOSFET,主要用于中压和低压领域;SJ-(超结)MOSFET,主要在高压领域应用。

其中,SGT MOSFET结构具有电荷耦合效应,在传统沟槽型MOSFET器件PN结垂直耗尽的基础上引入了水平耗尽,在采用同样掺杂浓度的外延材料规格情况下,器件可以获得更高的击穿电压。较深的沟槽深度,可以利用更多的硅体积来吸收EAS(Energy AvalancheStress,雪崩能量测试)能量,所以SGT在雪崩时更能承受雪崩击穿和浪涌电流。在开关电源、电机控制、动力电池系统等应用领域中,SGT MOSFET配合先进封装,非常有助于提高系统的效能和功率密度。

MOS器件的阈值电压,是指器件的漏源刚好导通时的栅电压,阈值电压的大小需求主要是由应用的驱动电压来决定。阈值电压的稳定性非常重要,特别是在多MOS并联的应用中(如电机控制、BMS等),如果阈值电压差别较大,最高开启的器件会由于大电流而导致热失效。

在SGT工艺制造过程中,制造工艺会存在不稳定的现象,比如沟槽尺寸、沟槽深度、注入剂量和能量的稳定性,热过程的稳定性及介电层和通孔尺寸等等。而影响SGT阈值电压的主要因素有栅氧化层厚度和质量、杂质离子注入浓度、沟槽尺寸、通孔尺寸、热处理的均匀性以及一致性等。随着线宽等逐渐减小,沟槽尺寸、通孔尺寸等与阈值电压的相关性越来强,对于沟槽尺寸和通孔尺寸的控制和搭配也变得更为重要。

发明内容

基于此,本发明旨在解决现有技术中,由沟槽尺寸和通孔尺寸波动和不匹配引起的阈值电压的大幅波动的问题。工艺方法包括:

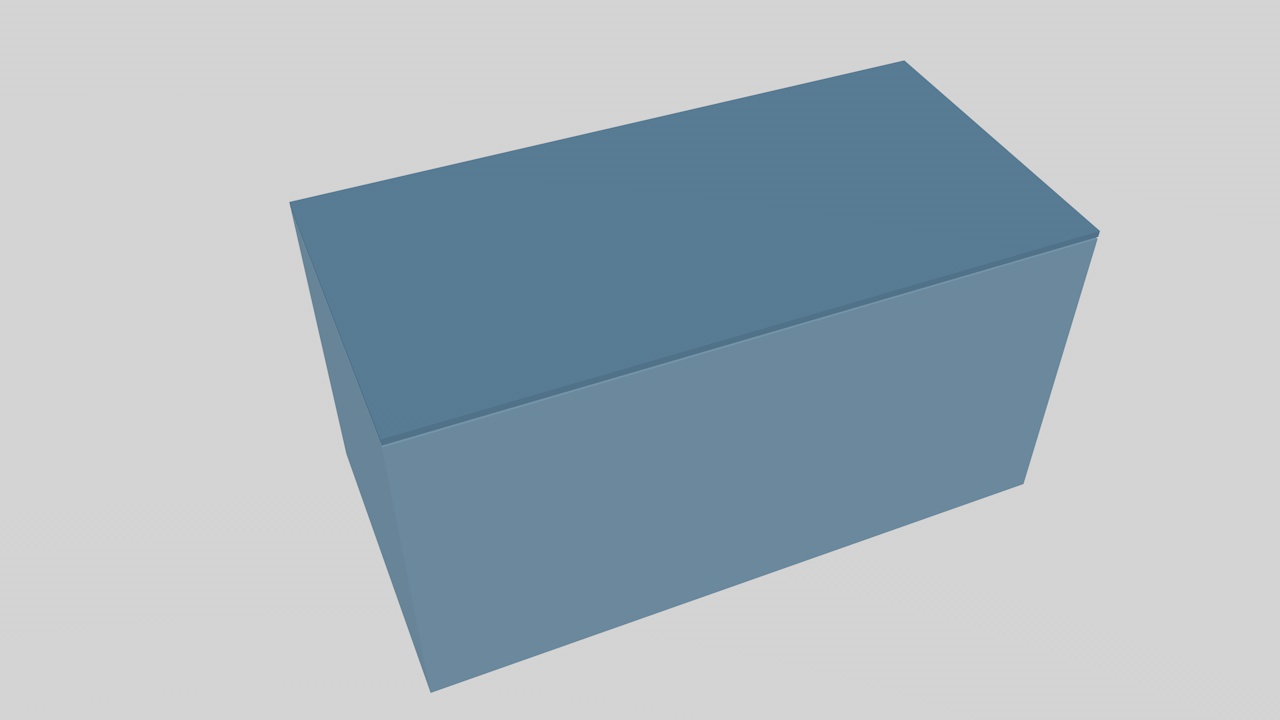

1、提供一外延衬底,并在外延衬底上沉积具有复合结构的掩膜层;

2、在沉积有掩膜层的外延衬底上进行蚀刻,以形成沟槽;

3、获取第一目标值,并对沟槽的宽度进行测量,得到沟槽宽度值,将沟槽宽度值与第一目标值作差,得到第一差值;

4、将第一差值输入映射模型中,输出对应的第一目标档位。此前,要建立预设范围值与各第一目标档位的映射关系,以得到映射模型,映射模型用于输入一具体值,输出其所在预设范围值对应的第一目标档位。第一目标档位包括三个子档位,第一子档位对应的预设范围值为[-0.1μm,-0.05μm],第二子档位对应的预设范围值为(-0.05μm,0.05μm),第三子档位对应的预设范围值为[0.05μm,0.1μm]。

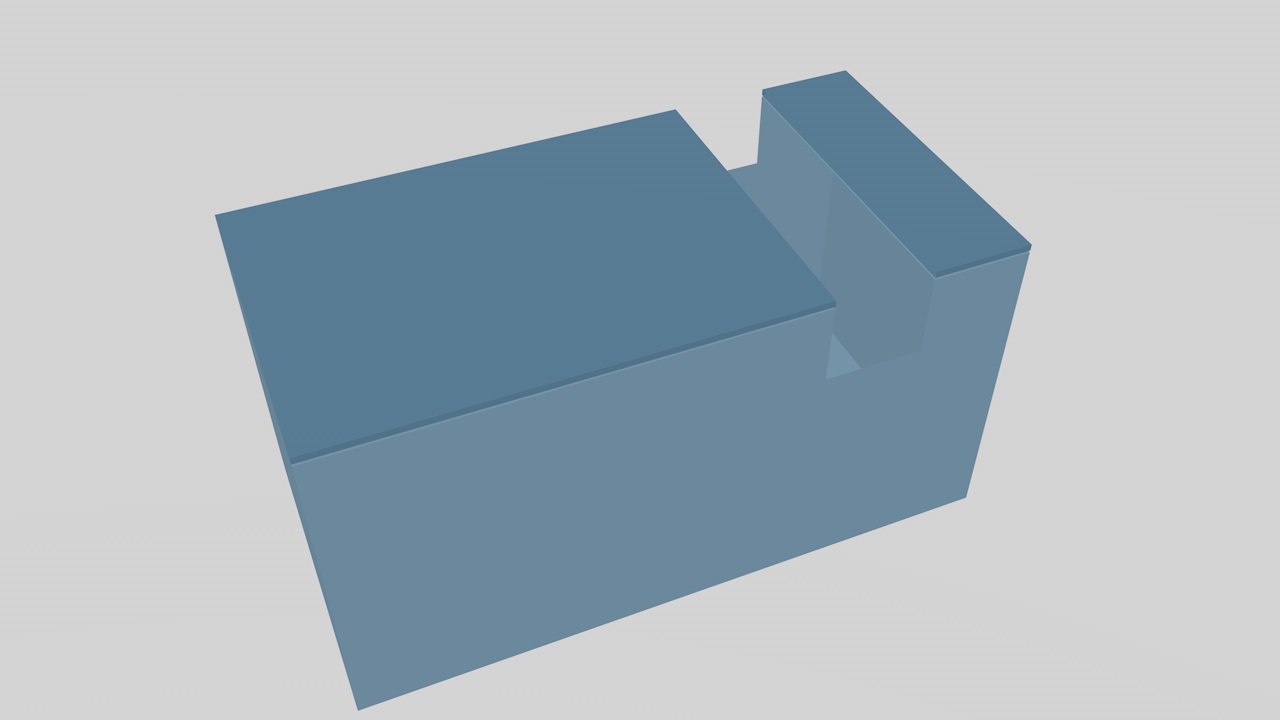

5、在沟槽中形成栅极,然后控制源极离子注入,并根据第一目标档位,调用对应的光刻程序,以对通孔的刻蚀进行控制。具体细分为:

(1)通过热氧化的方式,在沟槽内壁生长第一氧化层,第一氧化层作为屏蔽栅侧壁的介质层。第一氧化层的生长温度为800℃~1100℃,生长厚度为4000Å~6000Å;

(2)在沟槽内填充屏蔽栅多晶硅,并采用CMP技术磨平后回刻,以在沟槽内形成屏蔽栅;

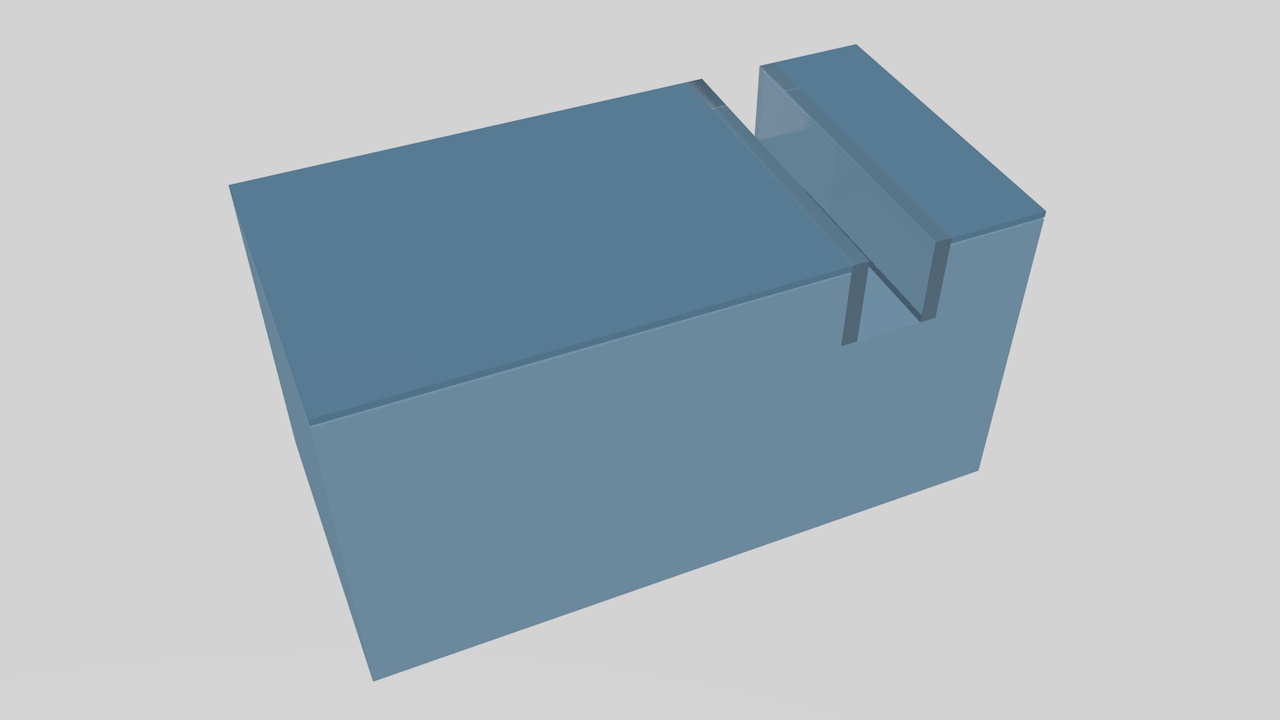

(3)采用湿法刻蚀技术将侧壁的介质层刻蚀预设深度,填充栅极与屏蔽栅之间的隔离氧化层,然后通过热氧化生长第二氧化层,以形成栅氧化层。预设深度为1.5μm~2.5μm,第二氧化层的厚度为400Å~600Å;

(4)在第二氧化层上沉积多晶硅,以使多晶硅填满沟槽,并采用CMP技术磨平,以完成栅极的制作。

6、获取第二目标值,并对通孔的宽度进行测量,得到通孔宽度值,将通孔宽度值与第二目标值作差,得到第二差值;

7、将第二差值输入映射模型中,输出对应的第二目标档位。第二目标档位包括三个子档位,第一子档位对应的预设范围值为[-0.15μm,-0.05μm],第二子档位对应的预设范围值为(-0.05μm,0.05μm),第三子档位对应的预设范围值为[0.05μm,0.15μm]。

8、判断第一目标档位与第二目标档位是否为同一档位;

若是,则控制工艺流程结束;

若否,则重新调试光刻程序,以使最终刻蚀的第一差值和第二差值所属档位相同。

改善效果

通过控制沟槽尺寸和通孔尺寸波动和不匹配,从而有效改善阈值电压的稳定性。

具体实施方式

第一差值 (μm) | 第二差值 (μm) | 阈值电压 (mV) | 阈值电压变化(%) | |

实施例1 | 0 | 0 | 3.1 | 0 |

实施例2 | 0.06 | 0.05 | 3.13 | 0.97 |

实施例3 | 0.02 | 0.02 | 3.12 | 0.65 |

实施例4 | -0.02 | -0.02 | 3.08 | -0.65 |

实施例5 | -0.06 | -0.05 | 3.12 | 0.65 |

实施例6 | 0.06 | 0 | 3.22 | 3.87 |

实施例7 | -0.05 | -0.12 | 2.96 | -4.52 |

实施例8 | 0.05 | 0.15 | 3.25 | 4.84 |

实施例9 | -0.02 | -0.03 | 3.07 | -0.97 |

实施例10 | 0 | 0.02 | 3.12 | 0.65 |

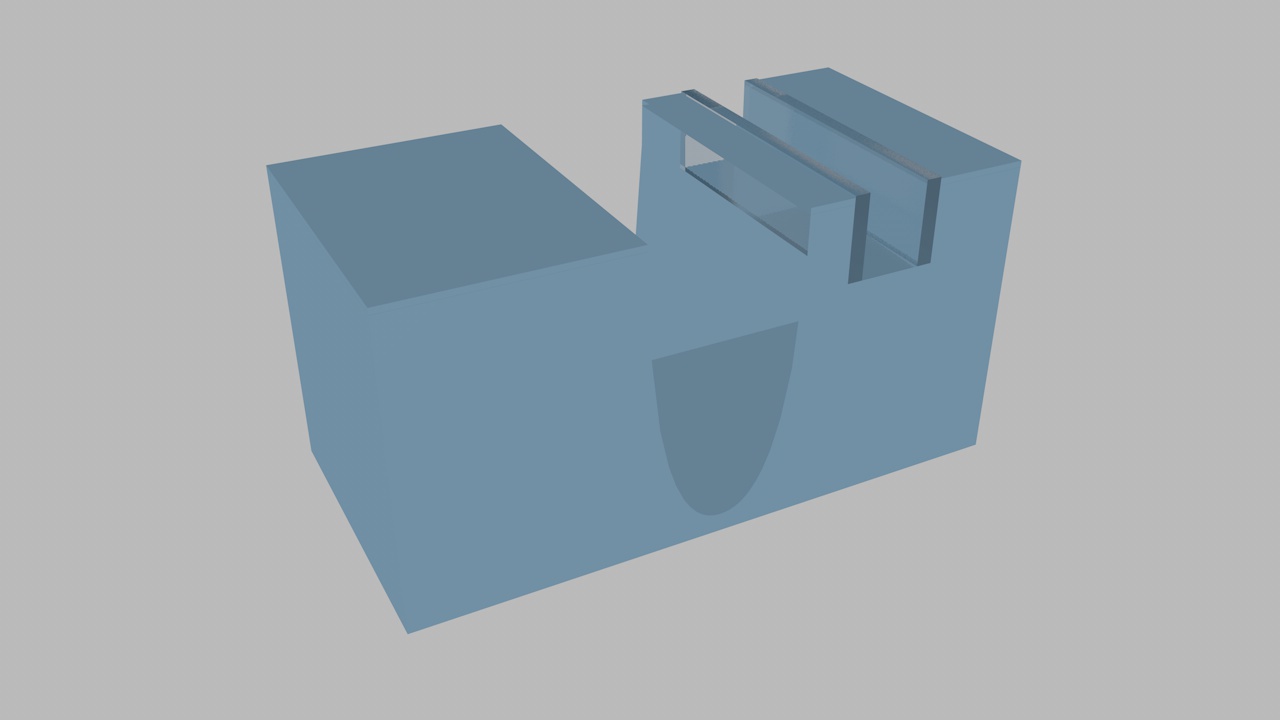

在SGT MOS生产工艺中,为了降低接触电阻,通过降低基区的电阻,从而可以提升芯片抗电流冲击能力,在通孔这一工艺中,需要进行重掺杂离子注入及热处理,由于芯片上重复单元的尺寸越来越小,离子将扩散到沟道附近,影响阈值电压。其中,沟槽尺寸大小会影响有源区的大小,进而影响通孔到沟道的距离,从而影响阈值电压的稳定性。

S01:提供一外延衬底,并在外延衬底上沉积具有复合结构的掩膜层;

具体的,首先提供一外延衬底,可以为硅衬底,外延衬底不限定N衬底或P衬底,并在外延衬底上沉积具有复合结构的掩膜层,其中,掩膜层依次由第一氧化层、氮化层以及第二氧化层组成,也即ONO(氧化层/氮化层/氧化层)结构,氮化层为氮化硅,其中,氧化层与基晶的结合较氮化层好,而氮化层居中,则可阻挡缺陷的延展,故此三层结构可互补所缺。

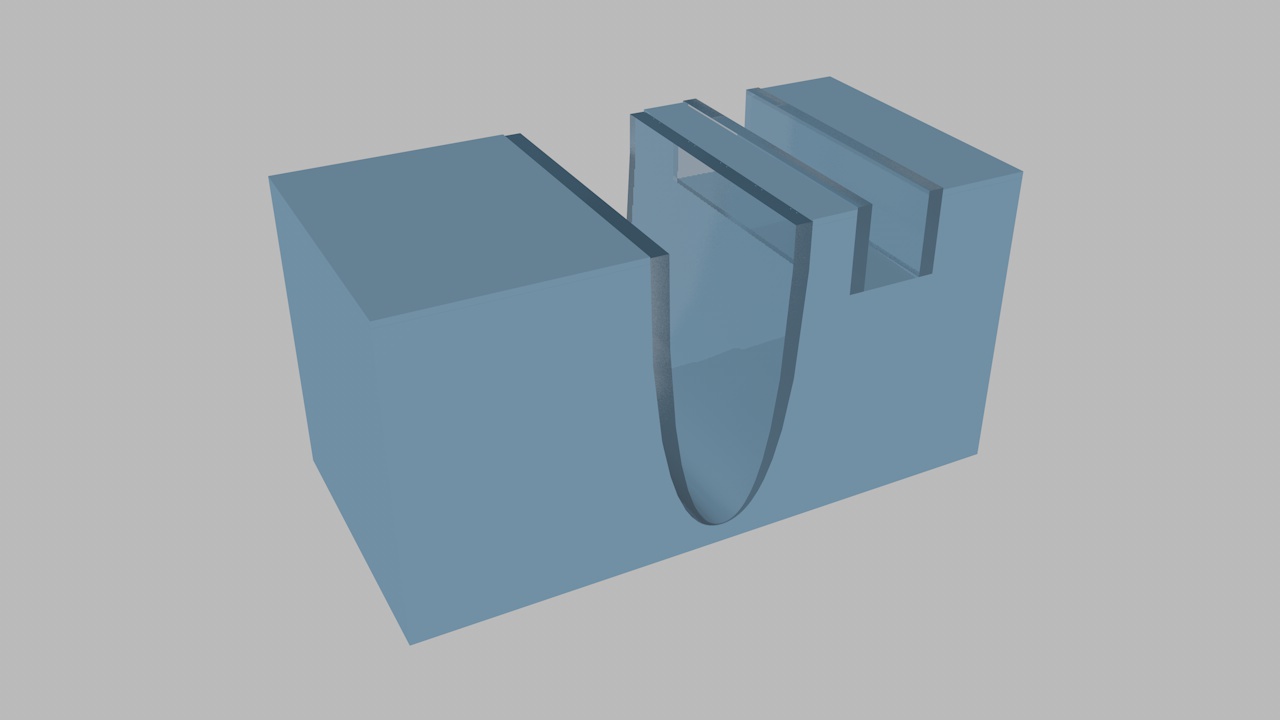

当掩膜层制备完成后,在沉积有掩膜层的外延衬底上进行蚀刻,以形成沟槽。沟槽越深,蚀刻时所需的光阻就越厚,但是,光阻太厚曝光后容易倒掉,因此,需要掩膜层来替代光阻的作用,以此减薄光阻,除了刻蚀沟槽外,还可以作为CMP以及HDP的阻挡层,以保护衬底表面不会被损伤。

第一目标值为沟槽在设计时的理论宽度值,当形成沟槽后,可以通过图像识别的方式,先对沟槽进行拍摄,然后对拍摄得到的沟槽图片进行识别,以获取沟槽宽度值,或者使用金相显微镜,通过人工的方式对沟槽宽度进行测量,以获取沟槽宽度值,再将沟槽宽度值与理论宽度值作差,得到第一差值。

在将第一差值输入映射模型之前,先要建立映射模型,其中,建立预设范围值与各第一目标档位的映射关系,以得到映射模型,映射模型用于输入一具体值,输出其所在预设范围值对应的第一目标档位。

为了确保通孔与沟槽(导电沟道)的距离保持不变,通过根据不同的沟槽宽度,调节通孔曝光时的工艺程序,相应的改变通孔的宽度,这样就能补偿沟槽宽度带来的影响。