发布时间:2024-04-15 | ![]() 浏览量:147

浏览量:147

技术领域

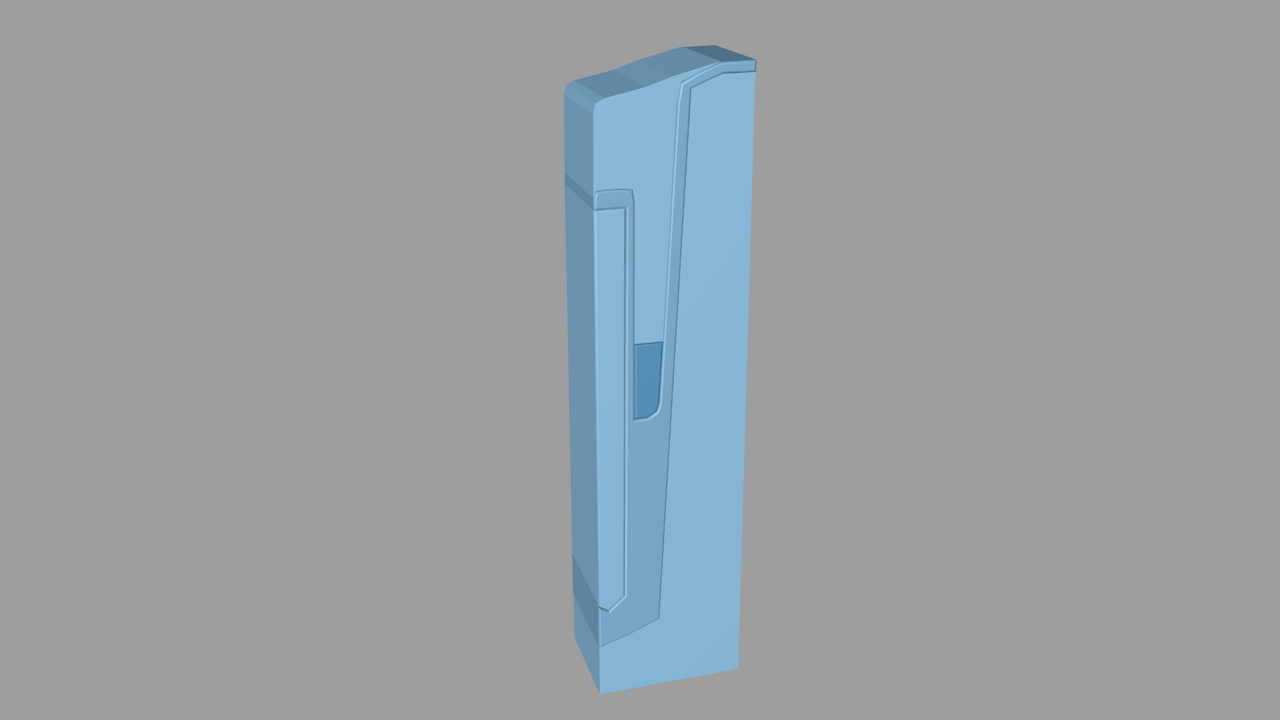

本发明涉及半导体器件制造的技术领域,特别涉及一种SGT器件的工艺方法及SGT器件。

背景技术

MOSFET大致可以分为以下几类:(1)平面型MOSFET;(2)Trench (沟槽型)MOSFET,主要用于低压领域;(3)SGT(Shielded Gate Transistor,屏蔽栅沟槽)MOSFET,主要用于中压和低压领域;(4)SJ-(超结)MOSFET,主要在高压领域应用。

其中,SGT MOSFET结构具有电荷耦合效应,在传统沟槽型MOSFET器件PN结垂直耗尽的基础上引入了水平耗尽,在采用同样掺杂浓度的外延材料情况下,器件可以获得更高的击穿电压。较深的沟槽深度,可以利用更多的硅体积来吸收EAS(Energy AvalancheStress,雪崩能量测试)能量,所以SGT在雪崩时更能承受雪崩击穿和浪涌电流。在开关电源、电机控制、动力电池系统等应用领域中,SGT MOSFET配合先进封装,大大提高了系统的效能和功率密度。

在常规工艺中,SGT的形成是在外延衬底上挖好沟槽后,先通过热氧形成侧壁氧化层,然后向沟槽填充多晶硅,将多晶硅往下蚀刻形成屏蔽栅,然后再用湿法蚀刻去除侧壁的氧化层,再通过氧化生成栅氧后再填充多晶硅形成栅极,这种工艺得到的SGT电场强度的尖峰在阱区与EPI(通过外延技术生长的硅)形成的PN结与沟槽底部处。

SGT的耐压可以用电场强度曲线延沟槽方向的积分面积来表征,积分面积越大,耐压越高。传统的SGT虽然引入了水平耗尽,但是电场强度的尖峰在阱区与EPI形成的PN结与沟槽底部处,电场强度分布呈“M”型,中间的部分有凹陷,使得耐压能力受限。

发明内容

基于此,本发明的目的是提供一种SGT器件的工艺方法及SGT器件,旨在解决上述技术问题。工艺方法包括:

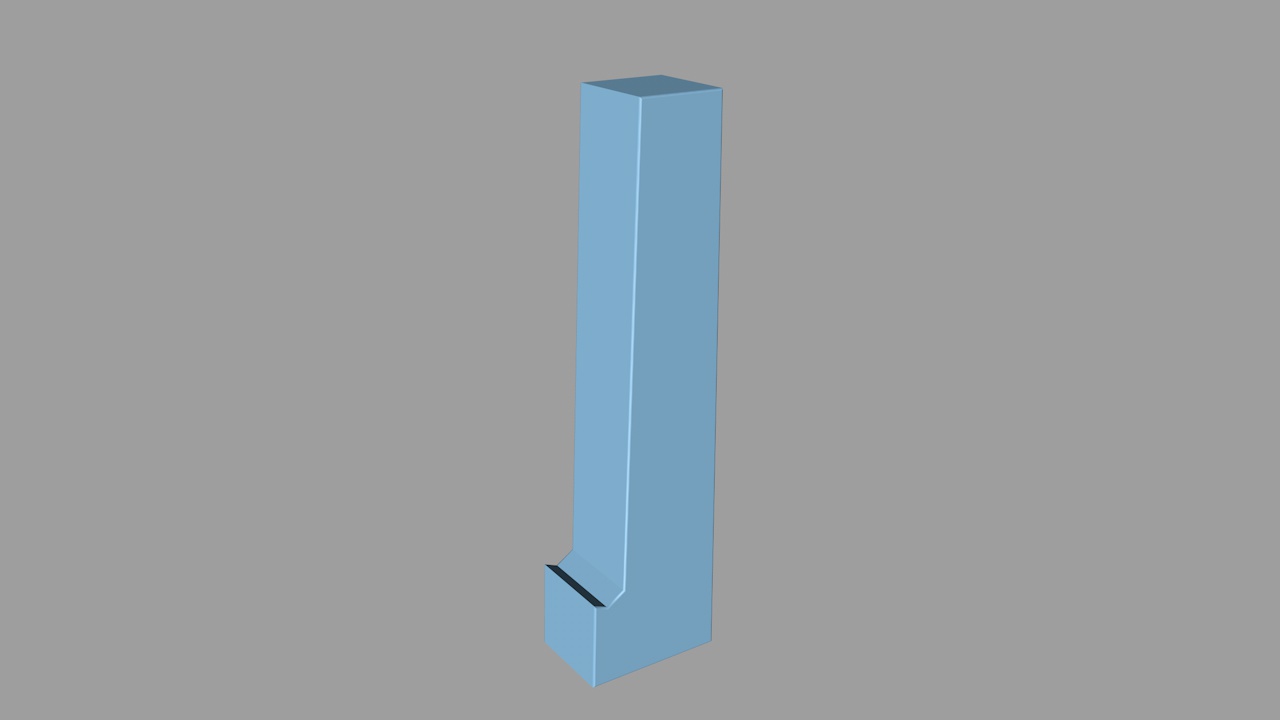

1、提供一N型外延衬底1,并在其上进行刻蚀,得到具有第一沟槽的N型外延衬底。第一沟槽的深度为5.5μm~6.5μm。

2、通过热氧化的方式,在第一沟槽内壁生长第一氧化层2。在温度为800℃~1000℃的条件下通入氧气,生长厚度为5600Å~6500Å,作为后续屏蔽栅与N型外延衬底1的有效隔离。若厚度太薄,则会导致隔离效果不好,若太厚,则在后续的多晶硅填充时,中间会有空隙产生,影响SGT器件质量。

3、在具有第一氧化层的第一沟槽内填充N型掺杂的多晶硅,并采用CMP技术磨平后回刻,以在第一沟槽内形成屏蔽栅3。屏蔽栅表面与N型外延衬底表面的距离为1.3μm~1.7μm。其中,屏蔽栅可以作为水平方向耗尽的场板。

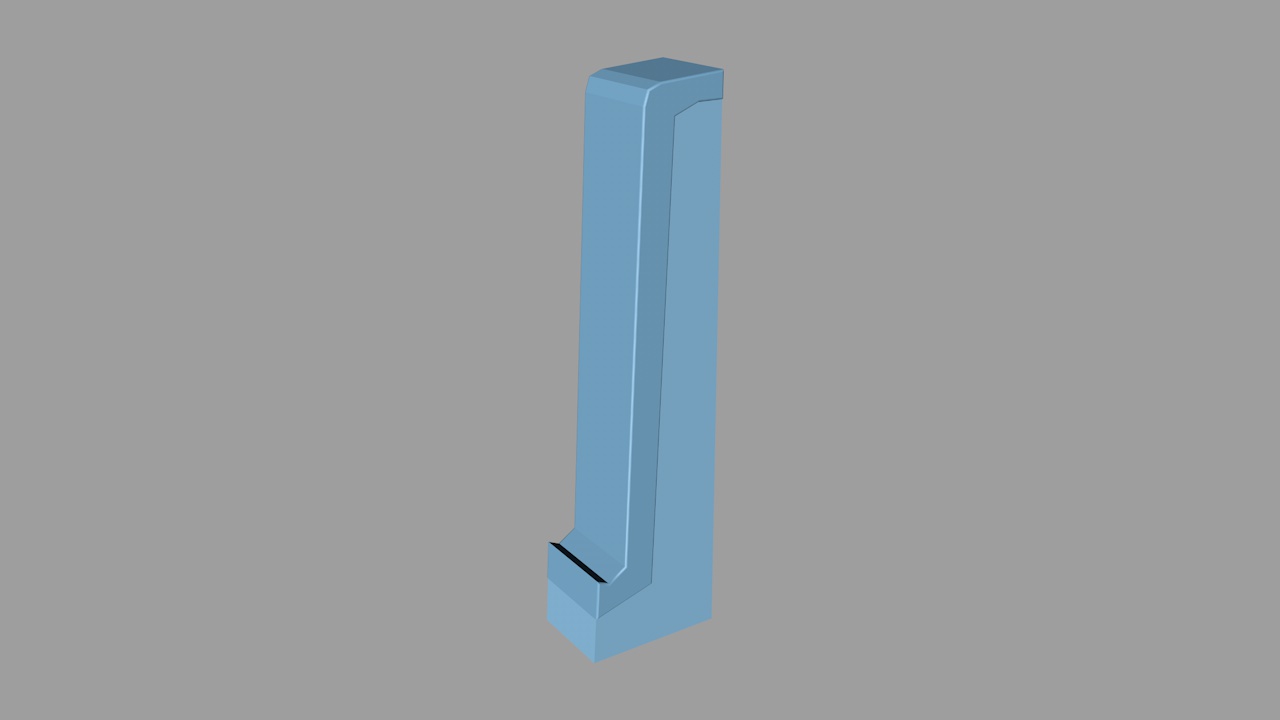

4、采用湿法刻蚀技术,将第一沟槽内壁的第一氧化层刻蚀预设深度2.5μm~3.5μm,以形成用于后续填充P型掺杂的多晶硅的第二沟槽。第二沟槽的底部位于第一沟槽深度方向上的中间区域。

5、通过热氧化的方式,在第二沟槽内壁生长预设厚度的第二氧化层。第二氧化层即为栅氧化层,厚度为400Å~600Å。

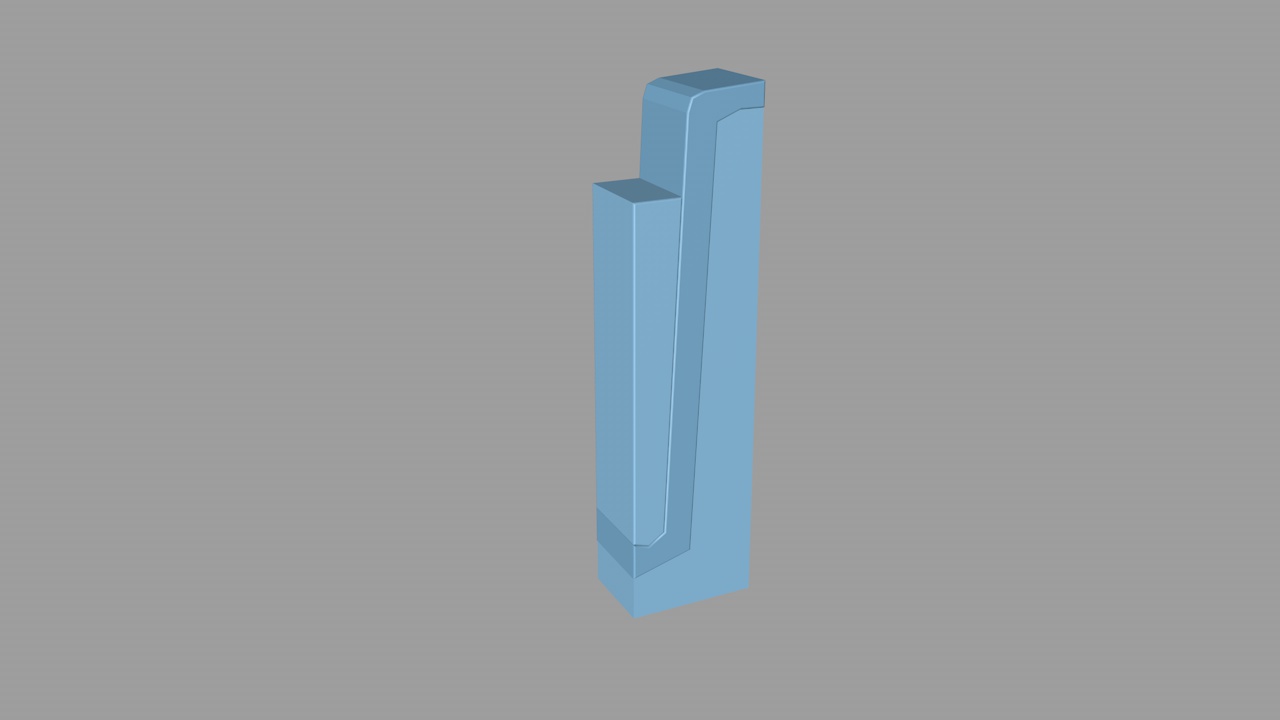

6、将P型掺杂的多晶硅和N型掺杂的多晶硅依次沉积于第二沟槽内。P型掺杂的多晶硅为掺杂硼的多晶硅,硼的掺杂浓度为1017atoms/cm3~1021atoms/ cm3。N型掺杂的多晶硅沉积的厚度为1.2μm~1.4μm。P型掺杂的多晶硅4作为后续杂质的扩散源,通过其侧壁的栅氧化层,即第二氧化层,扩散到旁边的EPI(采用外延生长的硅)衬底中,即N型外延衬底1。回刻后,在上方沉积 1.2μm~1.4μm的N型掺杂的多晶硅5,形成栅极。采用CMP技术磨平。

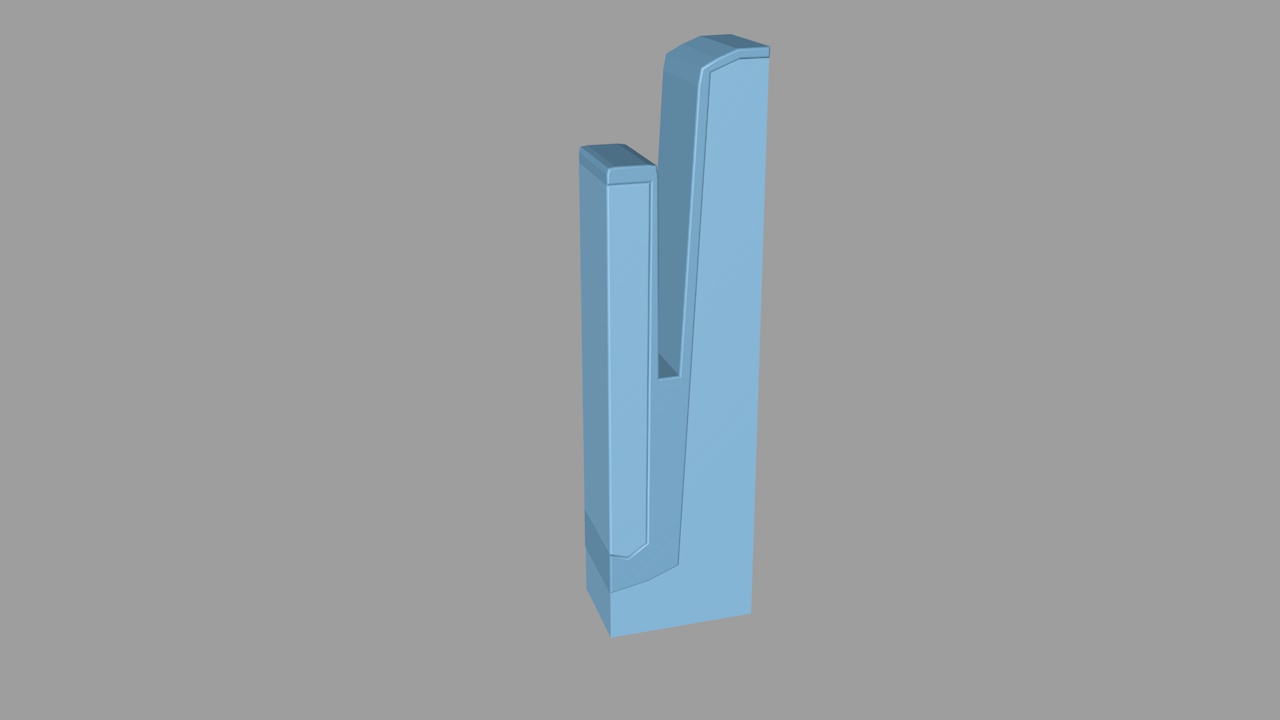

7、阱掺杂后,在温度为800℃~1000℃进行退火,此时,之前沉积的P型掺杂的多晶硅中的硼,会通过侧壁的栅氧化层扩散到旁边的N型外延衬底中,以此形成PN结, SGT沟槽中部区域水平方向的耗尽增强,具有高击穿电压的SGT器件产生。

发明效果

通过形成第二沟槽,并增强第二沟槽中部位置侧面的mesa(沟槽旁边的衬底)耗尽,在阱区与N型外延衬底形成的PN结与沟槽底部两个位置的中间再增加一个电场强度尖峰,来提高电场强度曲线延沟槽方向的积分面积,从而达到提高SGT击穿电压的效果。

实施案例

第一沟槽深度(μm) | 第一氧化层生长厚度(Å) | 第一氧化层生长温度(℃) | 表面距离(μm) | 第二氧化层刻蚀深度(μm) | 第二氧化层生长厚度(Å) | 硼的掺杂浓度(atoms/ cm3) | P型掺杂的多晶硅沉积厚度(μm) | 退火温度(℃) | 击穿电压(V) | |

实施例1 | 5.5 | 5600 | 800 | 1.3 | 2.5 | 400 | 1017 | 1.2 | 800 | 113 |

实施例2 | 5.5 | 5600 | 800 | 1.3 | 3 | 400 | 1017 | 1.2 | 800 | 114 |

实施例3 | 5.5 | 5600 | 800 | 1.3 | 3.5 | 400 | 1017 | 1.2 | 800 | 114 |

实施例4 | 6 | 5900 | 900 | 1.5 | 3 | 500 | 1018 | 1.3 | 900 | 114 |

实施例5 | 6.5 | 6200 | 1000 | 1.7 | 3 | 600 | 1019 | 1.4 | 1000 | 114 |

实施例6 | 5.5 | 5600 | 800 | 1.3 | 3 | 400 | 1021 | 1.2 | 800 | 112 |

对比例1 | / | / | / | / | / | / | / | / | / | 110 |

对比例2 | 6.5 | 5600 | 800 | 1.3 | 2 | 400 | 1017 | 1.2 | 800 | 106 |

对比例1提供一种SGT器件,通过传统工艺制备得到。对比例2与实施例1的区别在于,步骤4中,采用湿法刻蚀技术,将第一沟槽内壁的第一氧化层刻蚀2μm,以形成用于后续填充P型掺杂的多晶硅的第二沟槽。

经过100V的击穿电压测试,有结论:采用本发明实施例中的方法制备得到的SGT器件的击穿电压得到明显改善,最高击穿电压可达114V,而对比例1和对比例2中制备得到的SGT器件的击穿电压仅分别为110V和106V。

具体的,第一氧化层刻蚀深度3μm时的击穿电压,比2.5μm时要高。而当超过3μm时,击穿电压无进一步改善。当小于2.5μm时,击穿电压下降。

在对比例1中,只将N型掺杂的多晶硅沉积于第二沟槽内,而未填充P型掺杂的多晶硅时,SGT器件的击穿电压比对比例1中的稍好。

另外,在实施例6中,在其它条件不变的情况下,当硼的掺杂浓度过高,SGT器件的击穿电压反而会下降。